Технические энтузиасты провели полную разборку одного из процессоров серии Ryzen 9000 (Granite Ridge) и поделились высокодетализированными изображениями кристаллов CCD (с ядрами Zen 5) и cIOD (ввода-вывода) новых процессоров.

Источник изображений: X / @FritzchensFritz

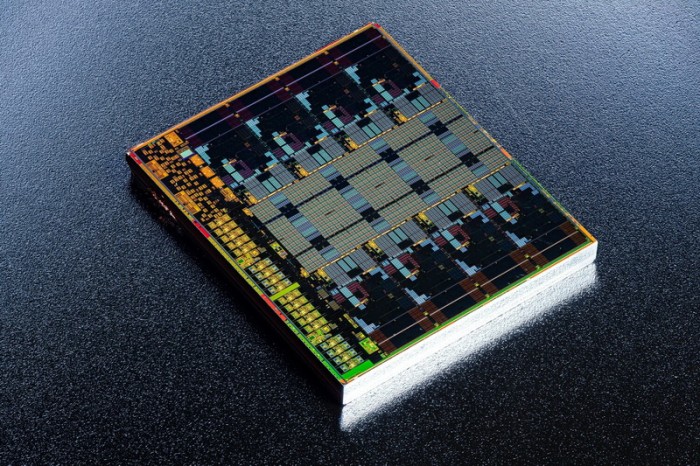

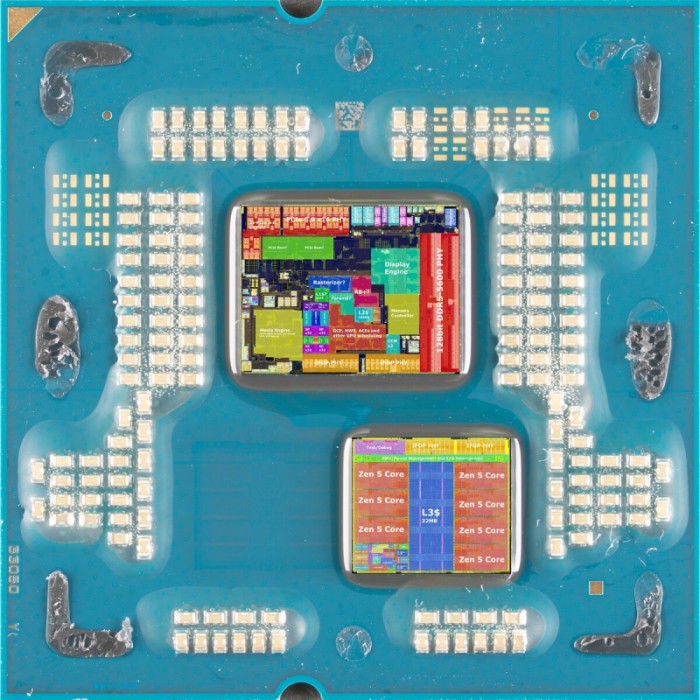

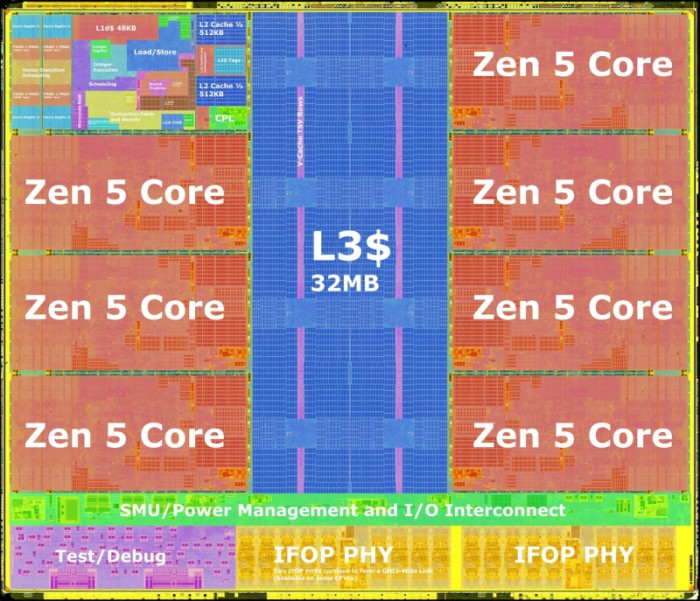

Упаковка новых чипов похожа на упаковку предшественников Ryzen 7000 (Raphael). В зависимости от модели чип может содержать один или два восьмиядерных чиплетов CCD, а также один кристалл ввода-вывода (cIOD), располагающийся в центральной части процессорной платы. Кристалл cIOD новые Ryzen 9000 позаимствовали у предшественников. Таким образом AMD удалось снизить затраты на разработку новых чипов. Кристаллы CCD с ядрами Zen 5 производятся с применением 4-нм техпроцесса TSMC N4P.

Ядра в составе CCD процессоров Granite Ridge расположены ближе друг к другу, чем в CCD процессоров Raphael на Zen 4. Каждый CCD Granite Ridge содержит по 8 полноразмерных ядер Zen 5, в составе каждого из которых имеется по 1 Мбайт кеш-памяти L2. В центральной части CCD расположены 32 Мбайт кеш-памяти L3, распределяющиеся между ядрами. Другими компонентом CCD является контроллер управления SMU (System Management Unit) и физическая реализация шины Infinity Fabric over Package (IFoP), которая нужна для соединения чиплетов CCD и cIOD.

Блок CCD с ядрами Zen 5 процессоров Ryzen 9000

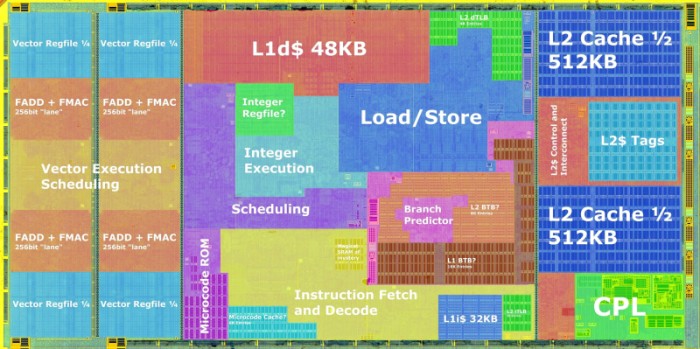

Каждое ядро Zen 5 по размерам больше, чем Zen 4 (производится с применением техпроцесса TSMC N5), ввиду использования блока FPU с врождённой поддержкой 512-битных данных для AVX-512. Векторный движок (Vector Engine) вынесен к самому краю ядра. Это имеет смысл, поскольку FPU является самым горячим компонентом ядра CPU. На другом краю ядра, ближе к общему L3-кешу находятся два блока кеш-памяти L2 по 512 Кбайт. AMD удвоила пропускную способность и ассоциативность этой кеш-памяти по сравнению с Zen 4.

Схема ядра Zen 5

В центральной области Zen 5 находятся 32 Кбайт кеш-памяти L1I, 48 Кбайт кеш-памяти L1D, целочисленные исполнительные устройства (Integer Execution Engine), а также входная часть конвейера процессора с блоком выборки и декодирования инструкций (Instruction Fetch & Decode), блоком прогнозирования ветвлений (Branch Prediction Unit), кешем микроопераций и планировщиком (Scheduler).

Кеш L3 в центральной части кристалла CCD объёмом 32 Мбайт имеет ряды TSV (сквозные кремниевые переходные отверстия), которые служат заделом для потенциальной «склейки» с дополнительным кристаллом кеша 3D V-Cache. Кристалл 3D V-Cache объёмом 64 Мбайт с помощью этих TSV может быть подключен напрямую к внутренней кольцевой шине CCD.

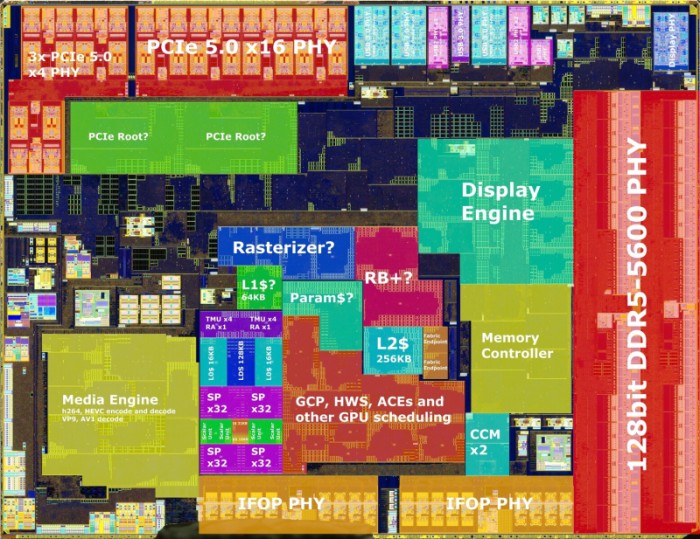

Кристалл cIOD в составе новых процессоров производится с применением 6-нм техпроцесса TSMC N6. Примерно 1/3 его площади занимает встроенный блок iGPU и его смежные компоненты, такие как мультимедийный движок и механизм отображения.

Блок cIOD

iGPU, как и ранее, основан на графической архитектуре RDNA 2 и оснащён всего одной группой процессоров рабочих групп (WGP) с двумя исполнительными блоками (CU) или 128 потоковыми процессорами. Другим ключевым компонентом cIOD является интерфейс PCIe Gen 5 с поддержкой 28 линий, два интерфейса IFoP для межкристального соединения с ядерными блоками CCD, довольно большой SoC I/O с поддержкой USB 3.x и других типов интерфейсов, а также одна из важнейших частей процессора — контроллер памяти DDR5 с двуканальным (с четырьмя подканалами) интерфейсом.

Источник: 3Dnews.ru