Taiwan Semiconductor Manufacturing Co. объявила о том, что разработка двух дополнительных технологических процессов, которые базируются на транзисторах с вертикально расположенным затвором (fin-shaped field-effect transistors, FinFETs), почти завершена. Две новые технологии относятся к классу 16 нм и предполагают дальнейшее снижение энергопотребления по сравнению с имеющимися. Кроме того, одна из технологий позволяет уменьшить размеры кристалла.

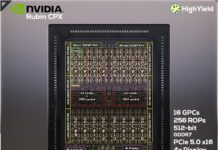

Ранее известные как 16-нм ULP [ultra-low power], технологические процессы 16 нм FinFET Compact (CLN16FFC) предназначены для производства микросхем со сверхнизким энергопотреблением, высокой плотностью транзисторов и высокой производительностью. Минимальное напряжение питания чипов, построенных при помощи CLN16FFC, будет равняться 0,55 В, что позволит создавать интегральные схемы со сверхнизким потреблением для носимых и Internet-of-things (IoT) устройств. Технологические характеристики CLN16FFC позволят производить с их помощью схемы с большим количеством транзисторов и умеренным энергопотреблением, что будет полезно для сложных мобильных систем на кристалле, графических и центральных процессоров.

Кремниевые подложки с микросхемами, произведённые TSMC

TSMC предложит клиентам две версии техпроцесса CLN16FFC: одна будет обладать плотностью транзисторов, сравнимой с технологическими процессами 16 нм FinFET (CLN16FF) и 16 нм FinFET+ (CLN16FF+); вторая будет предлагать увеличенную плотность транзисторов, что позволит уменьшить размеры микросхем. Судя по всему, все технологические процессы CLN16FF используют металлические межблочные соединения (back end of line, BEOL), разработанные для 20-нм технологического процесса TSMC (CLN20SOC). Однако в определённых случаях компании удалось добиться увеличения плотности транзисторов за счёт разного рода оптимизаций (в частности, уменьшения размеров ячеек SRAM, допустимых минимальных параметров соединений и т. п.), не влияющих существенно на правила проектирования и технологию изготовления. Тем не менее, чтобы произвести микросхему, спроектированную для CLN16FF+, при помощи новой технологии, некоторые элементы чипов придётся перепроектировать. Помимо прочего, CLN16FFC позволит немного сократить цикл производства FinFET-микросхем, который составляет сейчас 90 и более дней.

«Сегодня мы завершили первый этап [тестирования] CLN16FFC и получили хороший результат», — сказал Марк Ли (Mark Liu), президент и соисполнительный директор TSMC, в ходе телефонной конференции с инвесторами и финансовыми аналитиками. «До конца 2016 года мы произведём в кремнии около 100 проектов от 40 клиентов по техпроцессам CLN16FF+ и CLN16FFC, включая микросхемы для мобильных телефонов, сетевого оборудования, программируемых матриц и графических карт. Мы считаем, что наш 16-нм портфель [технологий], в том числе [технологии] CLN16FF+ и CLN16FFC, является весьма конкурентоспособным».

Специалист TSMC держит в руках фотомаску

TSMC не раскрывает сроков начала производства микросхем по технологическим процессам CLN16FFC. Учитывая, что набор для проектирования чипов по данному техпроцессу стал доступен в середине этого года, есть вероятность, что первые клиенты смогут получить «компактные» 16-нм схемы изготовленные TSMC в конце 2016 – начале 2017 года.

«Наш первоначальный график [выпуска CLN16FFC микросхем] на самом деле упоминал 2017 год, но мы могли бы ускорить, поскольку сейчас мы имеем две версии CLN16FFC», — сказал Си Си Вей (C.C. Wei), президент и соисполнительный директор TSMC. «Один из них сокращает размеры, второй нет».

В «чистой комнате» производственного комплекса TSMC Fab 14

Хотя планы TSMC в области техпроцесса CLN16FFC не до конца ясны, как не полностью понятны технические характеристики технологии, но довольно очевидно, что семейство 16-нм техпроцессов останется на рынке на очень долгий срок. Очень вероятно, что целый ряд клиентов Taiwan Semiconductor Manufacturing Co. предпочтут использовать в 2017 году опробованные технологические нормы CLN16FFC вместо нового и слабо известного им технологического процесса с транзисторным затвором 10 нм (CLN10FF).

Источник: 3Dnews.ru